AMDStrixHalo渲染揭示强大的RyzenAPU设计:16个Zen5核心、40个RDNA3+GPU核心、64MB缓存1

AMD的StrixHalo是更高端的RyzenAPU,它将为拥有多达16个Zen5核心和40个RDNA3+GPU核心的发烧级笔记本电脑提供动力,已在@Olrak_29发布的渲染图中透露。

AMDStrixHaloRender展示基于Chiplet的高端RyzenAPU,配备多达16个Zen5CPU核心和40个RDNA3+GPU核心

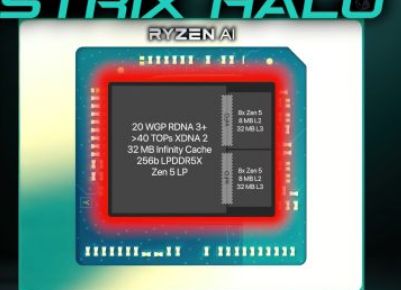

AMDStrixHaloAPU将成为小产品,采用最多3个、2个CCD和1个GCD。该将配备多达16个Zen5核心和32个线程。这些将保留相同的L1和L2缓存结构,因此L2缓存最大为16MB,而L3缓存将增加到每个CCD32MB。因此我们可以在顶部(两个CCD)上看到高达64MB的L3缓存。据说这些CCD与GraniteRidge上使用的CCD不同。此外,仅提到了GCD,这意味着封装上可能没有IOD。

事实上,根据渲染图,AMDStrixHaloAPU将在GCD中合并所有I/O块,GCD是三个中最大的一个。它将包含一个具有超过40个TOP的XDNA2AINPU、32MB无限缓存、256位LPDDR5X内存,并且看起来该上还将配备Zen5LP(低功耗)核心。GCD/IOD将使用InfinityFabric互连连接到双Zen5CCD。

对于iGPU方面,StrixHaloAPU将保留RDNA3+图形架构,但将配备20个WGP或40个计算单元。此外,为了在小设计上支持此类高端iGPU,IOD上还将配备额外的32MBMALL缓存,这将消除该超级iGPU的带宽瓶颈。

其他规格包括支持高达LPDDR5x-8000(256位)内存,以及能够提供超过70个TOP的AI“XDNA2”NPU。StrixHaloAPU将围绕最新的FP11平台展开。这些APU的TDP为70W(cTDP55W),并支持高达130W的峰值额定功率。

AMDRyzenAIHXStrixHalo预期功能:

Zen5小设计

多达16核

64MB共享L3缓存

40个RDNA3+计算单元

32MBMALL缓存(用于iGPU)

256位LPDDR5X-8000内存控制器

集成XDNA2引擎

多达70个AITOPS

16个PCIeGen4通道

2024年2小时发布(预计)

FP11平台(55W-130W)

在显示方面,AMDStrix和StrixHaloAPU都将配备eDP(DP2.1HBR3)和外部DP(DP2.1UHBR10)、USBCAlt-DP(DP2.1UHBR10)和USB4Alt-DP(DP2.1UHBR10))支持作为其媒体引擎的一部分。StrixHalo将支持DP2.1UHBR20。

AMD预计将在Computex2024主题演讲中正式宣布并推出其下一代Zen5“Ryzen”CPU产品组合,因此预计在不到一个月的时间内将获得更多信息。